11:15 am

Th13

## Novel packet architecture for ultrafast alloptical networks

Fabrizio Forghieri, Alberto Bononi, and Paul R. Prucnal, Department of Electrical Engineering, Princeton University, Princeton, New Jersey 08544

Optical sampling techniques<sup>1-3</sup> have recently been proposed for demodulating data streams at bit rates far beyond the speed of conventional photoreceivers. These techniques may be used in ultrafast all-optical packet-switching networks to read the header and to demodulate the packet. A synchronized sampling optical pulse is sent on the desired bit slot in the received packet to test whether a pulse is present or not. The sampler works as an optical AND gate that outputs the bit pulse if this is present and outputs no signal otherwise. The pulse out of the AND gate is then sent onto a photodiode, and just a single short pulse will have to be detected in a time much longer than the bit time. With a parallel bank of optical samplers, packet detection is converted into a parallel detection of deltalike spikes at a repetition rate suitable for electronic detection.

A novel packet structure is proposed here to simplify the header recognition and packet demultiplexing blocks. The header, instead of preceding the payload, is spread regularly across the packet in a TDM fashion. If the interleaving period between header bits is longer than the minimum electronic detection time, the header can be extracted by sending the packet into a single AND gate together with an optical sampling clock at the interleaving rate. For example, ATM standards require a 53-byte packet, 48 bytes of which are for the payload and 5 of which are for the header. By inserting one header bit every 10 payload bits, a 55-byte packet is obtained in which the two extra bytes added to the payload may be used for syn-

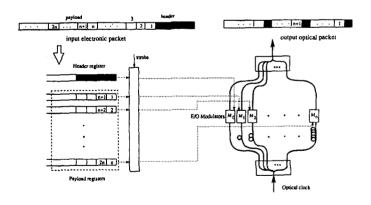

Th13 Fig. 1. Optical packet generation block.

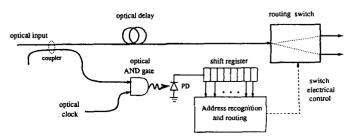

Th13 Fig. 2. Header recognition and packet routing.

chronization purposes. If the bit rate in the optical packet is 100 Gbit/s, the bit rate of the spread header is below 10 Gbit/s, low enough to be handled by conventional photoreceivers.

Figure 1 shows the optical packet generation block at the transmitter. The electronic input is a packet with h header bits and p payload bits, with p an integer multiple of h, p = nh. The header is extracted and serially fed into a dedicated shift register. The payload, instead, is sequentially separated into n parallel shift registers, as shown in the figure. This initial process can be done at electronic speed. A local optical clock generated by a mode-locked laser produces very short optical pulses at a repetition rate R = R/(n+1), where R is the bit rate in the optical packet. The clock output is split into (n + 1) branches to get one-bit shifted replicas of it, which are fed to an array of (n + 1)electro-optic (E/O) modulators. Once the electronic packet separation is complete, a strobe signal starts the optical packet modulation. The (n + 1) shift registers feed the parallel bank of modulators at a modulation rate equal to the clock rate  $R_{c}$ . The modulated optical pulses are recombined into a single stream to yield the optical packet in h clock periods.

Figure 2 details the header recognition at the node. A properly delayed version of the same optical clock used for packet generation is optically ANDEd with a replica of the received packet to extract the header bits, which are then detected onto a fast photodiode (PD) and stacked into a fast-access shift register. Processing of the register contents can be pipelined to perform the routing operations at electronic speed.<sup>4</sup>

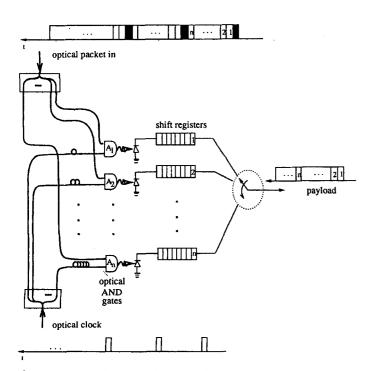

Figure 3 shows the scheme of the receiver. The same technique used to extract the header can be used to demultiplex and detect the payload. One-bit-shifted versions of the local sampling clock are sent to an array of n optical sampling gates together with the received packet, so that demultiplexing by a factor n is achieved. The n sampled sequences at rate  $R_i$  are separately sent onto fast photodiodes and are electronically buffered. The output of the n electronic shift registers is finally sequentially scanned to obtain parallel-to-serial conversion and to yield the received payload at lower electronic rates. The

ThI3 Fig. 3. Schematic diagram of the demultiplexer-receiver.

number of sampler n can be minimized for a given optical bit rate R by using the highest value of  $R_c$  allowed by the electronics.

- 1. M. N. Islam, Opt. Lett. 14, 1257 (1989).

- P. A. Andrekson, N. A. Olsson, J. R. Simpson, D. J. DiGiovanni, P. A. Morton, T. Tanbun-Ek, R. A. Logan, and K. W. Wecht, IEEE Photon. Technol. Lett. 4, 644 (1992).

- P. A. Andrekson, N. A. Olsson, M. Haner, J. R. Simpson, T. Tanbun-Ek, R. A. Logan, D. Coblentz, H. M. Presby, and K. W. Wecht, IEEE Photon. Technol. Lett. 4, 76 (1992).

- 4. P. R. Prucnal and P. A. Perrier, IEEE LCS 1, 54 (1990).